Η Taiwan Economic Daily twierdzi, że TSMC dokonał znaczącego wewnętrznego odkrycia w celu jego ostatecznej utylizacji technologia litograficzna 2 nm.

ΣWedług publikacji, ten kamień milowy pozwala TSMC na: jest optymistycznie nastawiony do wdrożenia wczesnej produkcji „Risk Production” 2 nm w 2023 r..

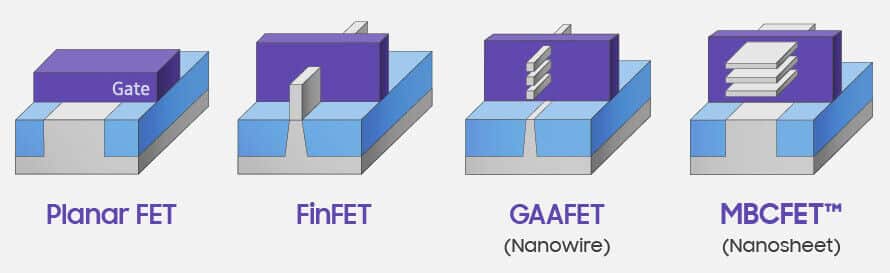

Wciąż imponujące są doniesienia, które TSMC rezygnuje z technologii FinFet na rzecz nowego wielomostkowego tranzystora polowego (MBCFET) oparty na technologii Gate-All-Around (GAA). To ważne odkrycie nadchodzi rok po utworzeniu przez TSMC zespołu halowego, którego celem było utorowanie drogi dla rozwoju litografii 2 nm.

Technologia MBCFET rozszerza architekturę GAAFET poprzez przekształcenie tranzystora polowego Nanowire w nanoarkusz. Główną ideą jest stworzenie tranzystora polowego XNUMXD.

Ten nowy półprzewodnikowy tranzystor z komplementarnym tlenkiem metali może poprawić sterowanie obwodami i zmniejszyć upływ prądu. Ta filozofia projektowania nie ogranicza się wyłącznie do TSMC - Samsung planuje opracować odmianę tego projektu w technologii litograficznej 3 nm.

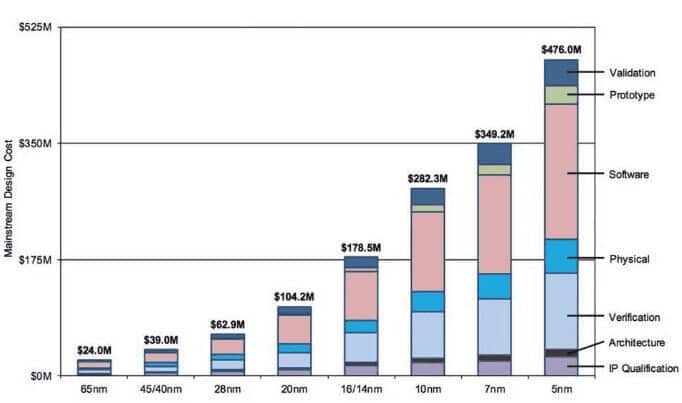

Jak zwykle, dalsza redukcja skali produkcji chipów wiąże się z ogromnymi kosztami. Konkretnie, koszt opracowania litografii 5 nm osiągnął już 476 milionów dolarów, podczas gdy Samsung twierdzi, że technologia GAA 3 nm będzie kosztować ponad 500 milionów dolarów. Oczywiście rozwój litografii 2 nm, przekroczy te kwoty…

Nie zapomnij tego przestrzegać Xiaomi-miui.gr w wiadomości Google być natychmiast informowanym o wszystkich naszych nowych artykułach!

Nie zapomnij tego przestrzegać Xiaomi-miui.gr w wiadomości Google być natychmiast informowanym o wszystkich naszych nowych artykułach!